Design-for-Test is becoming critical in ensuring the integrity of complex board performance and ensuring the maximum product lifecycle.

Traditionally, DfT is a specific post-layout process that is addressed by tools such as FABMaster and Teradyne D2B. The CAD file is loaded and a mechanical analysis is performed in order to identify the physical access restrictions for In-Circuit or Flying probe test.

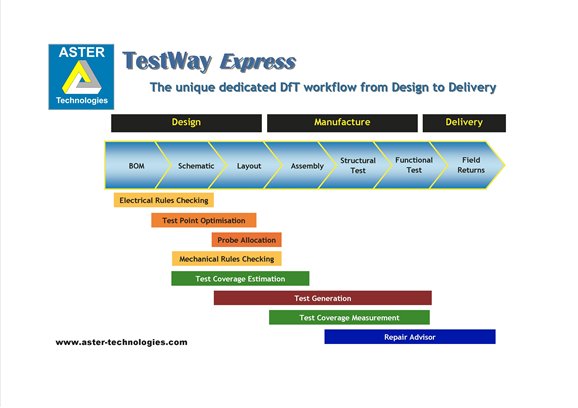

However, with the staggering board density we are now facing, DfT must be considered earlier and as part of the complete workflow, not just for probe placement. By verifying the testability at all stages we can ensure the highest level of test quality for the minimum test cost.

TestWay Express has been developed to meet this vision for a software tool that will allow users to analyze each stage of the design to delivery workflow within a single tool.

This is achieved by the following stages:

- The process starts at the Schematic design stage, verifying that optimum electrical DfT requirements and maximum test coverage is achieved.

- It will then optimize test probe placement according to test strategy definitions, estimate test coverage and cost modeling, calculate the production yield and TL9000 initial return rates.

- After PCB layout, TestWay Express will verify mechanical rules, allocate test probes and estimate test coverage based on the actual physical access.

- Finally, TestWay Express will generate the test programs, or input lists and test models, as well as test fixture files.

CAD importers supporting schematic netlist, layout, schematic graphics and design or test models are available for the wide range of EDA tools used within the industry today. This is a key differentiator from other commercial DfT tools that work only from the layout stage, which is often too late in the design process to be of use. TestWay Express operates directly from native CAD formats, ensuring the full interoperability between all stages across the design-manufacturing flow.

In the past, test engineers had to use multiple software tools to verify that a board had been designed with adequate testability. Once the test points had been validated it was still necessary to develop the ICT or flying probe test program files, which required another process stage.

With TestWay Express, all these stages are managed within a single tool using an integrated methodology.

Test coverage is estimated using theoretical models for a wide range of test and inspection strategies. These include Automated Placement Machines (APM), AOI, AXI, Boundary-scan Test (BST), Flying-probe Test (FPT), ICT and Functional Test. These models can be tuned to reflect the test and measurement capabilities of each individual target tester.

Once the test/inspection programs have been debugged and released, TestWay Express can read the completed test program or test report and compare the coverage between the estimated and measured analysis. The resultant analysis reports define the test coverage using industry standard metrics that enable the user to identify any misalignment between the estimated and real coverage.

Coverage importers are available for a wide range of the test/inspection machines used within the industry.

These include Acculogic (BS, Scorpion, SPRINT); Aeroflex (4200, 5800); Agilent Technologies (i1000, i3070, 5DX, SJ10, SJ50); ASSET; CHECKSUM; CORELIS; Cyberoptics, DrEschke; Europlacer;GOEPEL (CASCON, OPTICON); JTAG Technologies; Mirtec; MYDATA, OMRON; Orbotech; SAKI; SEICA; SPEA (3030, 4040); TAKAYA (APT8000, APT9000); Teradyne (Z1800, Spectrum, GR228x, TS124); TRI (TR7500, TR8001); VI Technology; VISCOM; XJTAG and YESTech. More are developed as required. www.aster-technologies.com