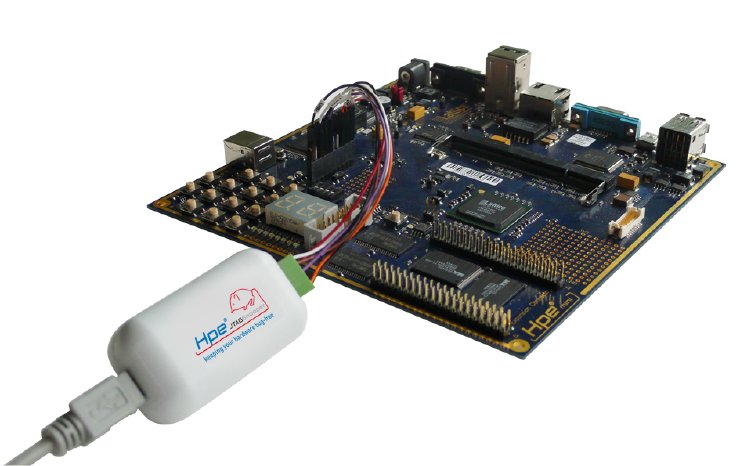

Hpe_JTAG is delivered with an optional USB-JTAG cable. It supports all obligatory JTAG instructions (SAMPLE, EXTEST, BYPASS) as well as INTEST. Additionally, arbitrary user register accesses can be defined.

To make it easier for users to locate relevant signals, signal names can be imported from BSDL or pin files, which were generated during the FPGA synthesis. As a result, it can be checked at a glance whether, for example, reset and enable signals are set correctly, clock inputs are toggling or data and address buses are stuck at a certain value. As opposed to measurements with an oscilloscope or logic analyzer this observation is absolutely non-intrusive.

A python scripting interface allows users to add functionality to the tool or to automate repetitive tasks. Any user defined JTAG access is allowed - users are only limited by their imagination.

A free demo version of Hpe_JTAG is available now and can be downloaded from:

http://www.ge-research.com/....

Entry level pricing of the full version is 399 Euro and during the embedded world 2009 only 359 Euro (plus VAT).