PowerPlay – effektives Power-Management

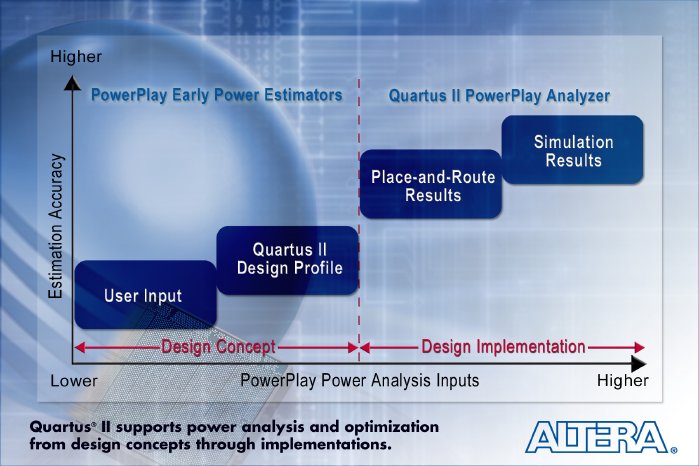

Mit der neuesten Version von Quartus II bietet Altera auch ein neues leistungsfähiges Tool für die Power-Analyse und -Optimierung: PowerPlay. Mit den Analyse-Funktionalitäten von PowerPlay kann die statische und dynamische Leistungsaufnahme genau abgeschätzt werden, wobei der Entwickler über den gesamten Design-Zyklus, von der Konzeption bis hin zur Implementierung, unterstützt wird.

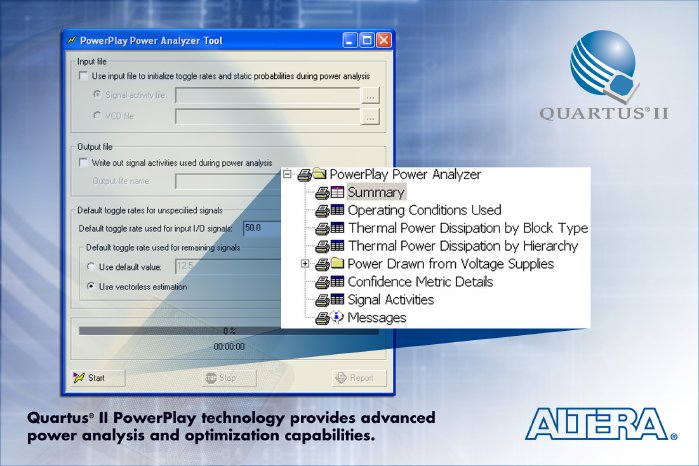

Mit dem „Easy Power Estimator“ kann die statische und dynamische Leistungsaufnahme für ein Projekt in einer ersten Annäherung abgeschätzt werden. Während der Implementierung können dann mit dem „Power Analyzer“ die Abschätzungen verfeinert werden. Eine noch präzisere Abschätzung wird durch die Verküpfung des vektorlosen Power-Analyse-Algorithmus mit den Place-and-Route-Ergebnissen erreicht. Wenn - optional - auch funktionale Simulationsvektoren oder Vektoren der Gate-Level-Simulation genutzt werden, können noch genauere Ergebnisse erzielt werden. Das PowerPlay-Analyse-Tool bietet auch einen sehr genauen Einblick in das Profil der Leistungsaufnahme, damit können Entwickler die gesamte Leistungsaufnahme im Hinblick auf die Design-Ressourcen und Hierarchie sehr genau prüfen. Mit den so gewonnen Daten lassen sich dann die Designs im Hinblick auf die entsprechenden Leistungs-Budgets optimieren.

Im Laufe des kommenden Jahres werden die PowerPlay-Tools zunehmend erweitert, u.a. mit automatisierten Optimierungswerkzeugen. Mit diesen PowerPlay-Optimierungstools können Entwickler die Leistungsaufnahme für ihre FPGA-, CPLD- und strukturierten ASIC-Designs effizient und automatisch optimieren.

Neben der PowerPlay-Technologie enthält die Version 4.2 über 100 neue Funktionen oder Verbesserungen für das Design von FPGAs, CPLDs oder strukturierten ASICs. Einige der neuen funktionellen Highlights sind:

• Neue Funktionen für die Implementierungs- und Timing-Analyse – Die neuen Funktionen dienen der Analyse und der Steuerung von Takt- und Daten-Versatz (Skew) sowie der Modellierung des Takt-Jitters. Außerdem ist eine bessere Analyse und Optimierung der Register-Steuerungssignale möglich.

• Multi-Clock-Domain-Unterstützung im SOPC Builder – Der SOPC Builder verfügt über neue Funktionen, die die einfache Systemintegration von Komponenten, die mit mehreren Clock-Domains arbeiten, unterstützen.

• Formale RTL/Gatter-Verifizierung – Neue Funktionen für die funktionelle Überprüfung bei der RTL-Gatter-Umsetzung mit der Cadence Conformal LEC Verifizierungssoftware.