Die Programmierung von FPGAs in OpenCL ist sehr attraktiv, weil sie in einer C-ähnlichen Hochsprache erfolgt und dennoch zu effizienten Implementierungen führt. Im Unterschied zur häufig ineffizienten Konvertierung von C-Programmen in VHDL beinhaltet OpenCL bereits die Beschreibung der Parallelisierung des Algorithmus und erlaubt eben dadurch eine effiziente Umsetzung auf die ja inhärent parallele FPGA-Architektur - typisch mit wesentlich schnellerer Ausführung als auf Standard-Prozessoren, und ohne den Aufwand einer Implementierung in VHDL.

Das Stratix V GX AB FPGA gehört mit 952.000 Equivalent Logic Elements zu den größten FPGAs von Altera. Das für digitale Signalverarbeitung optimierte Stratix V GS D8 FPGA enthält zwar "nur" 675.000 Equivalent Logic Elements, dafür aber mit 3.926 Multiplizierern und 1.963 DSP-Blöcken mehr als fünfmal so viele Rechenwerke wie die GX AB Variante. Beide eignen sich auch für sehr anspruchsvolle Aufgaben.

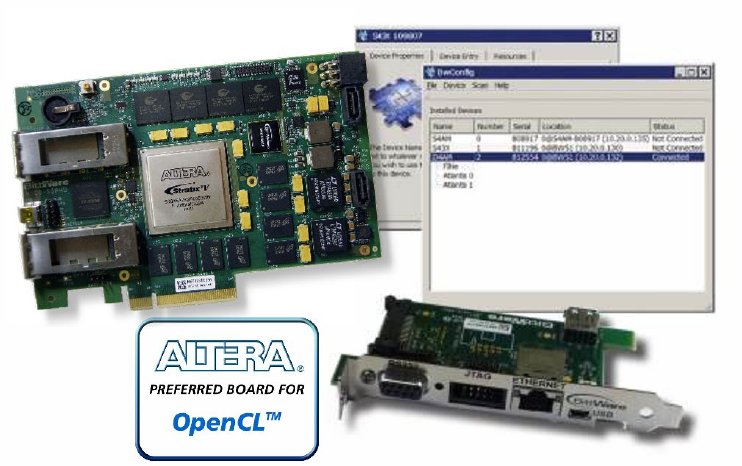

Geliefert werden die FPGAs auf BittWares S5PH-Q Karte, einer PCIe-3.0-Einsteckkarte halber Länge. Neben dem Stratix V FPGA (in den Varianten GX A7, GX AB, GS D5 oder GS D8) verfügt die Karte über 8 GB DDR3 SDRAM, eine PCIe-Schnittstelle, zwei QSFP-Cages für schnelle serielle Schnittstellen (z.B. 10 Gigabit Ethernet) in der Frontblende und verschiedene digitale Schnittstellen.

BittWares "OpenCL Development Bundle" ist ein komplettes FPGA-OpenCL-Entwicklungssystem aus einer Hand an, welches neben der FPGA-Karte alle benötigten Entwicklungstools inklusive der OpenCL-Entwicklungsumgebung beinhaltet. Es ist in allen Versionen ab sofort bei der A.R. Bayer DSP Systeme GmbH, www.dsp-systeme.net, Tel. +49 211 271 4630, erhältlich. Das Datenblatt ist unter downloads.dsp-sys.de/pr/ds-openCL.pdf verfügbar.