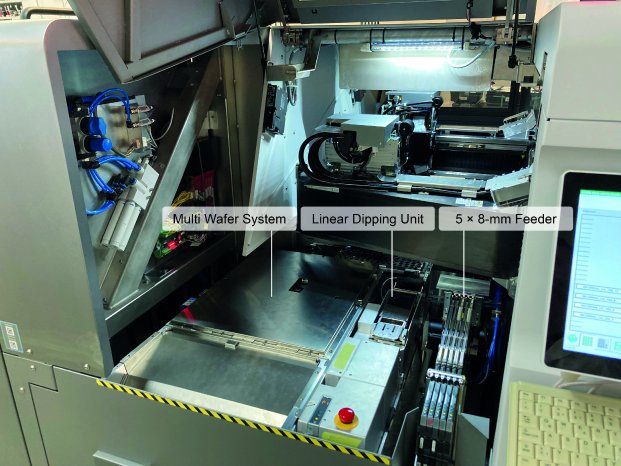

Bei der High-Volume-SiP-Fertigung, wie zum Beispiel für Smartphones und Tablets, werden einige Dies direkt vom gesägten Wafer verarbeitet, während andere Flip-Chips und Komponenten wie passive Bauelemente aus dem Gurt kommen. Bislang geschah dies in der Regel in zwei getrennten Prozessen. Mit der neuen hochflexiblen und leistungsstarken Bestückplattfom SIPLACE CA2 integriert ASMPT die Verarbeitung von Dies direkt vom gesägten Wafer mit in die SMT-Hochgeschwindigkeitslinie.

„Die SIPLACE CA2 bringt zusammen, was im SiP-Zeitalter zusammen gehört und erschließt damit neue Dimensionen im Advanced Packaging“, erklärt Sylvester Demmel, Senior Product Manager bei ASMPT SMT Solutions. „Die hochflexible Konfiguration und schlankere Prozesse schaffen neue Möglichkeiten, eröffnen Elektronikfertigern neue Märkte und Kundenkreise, steigern die Produktivität bei gleichzeitiger Kostensenkung und bringen damit deutliche Konkurrenzvorteile“.

Die-Puffer und Parallelisierung lösen Geschwindigkeitsprobleme

Eines der Haupthindernisse für die kombinierte SMT- und Die-Bestückung war bislang die relativ niedrige Verarbeitungsgeschwindigkeit der Dies direkt vom Wafer. Bei Wafern, die gesägt geliefert werden, sind die Dies auf einer Trägerfolie fixiert, von der sie für die Bestückung erst abgelöst werden müssen. Dieser Prozess lässt sich kaum beschleunigen.

Die SIPLACE CA2 löst dieses Problem durch einen Pufferspeicher mit ähnlichem Aufbau wie ein Bestückkopf, mit dem sich 16 neue Dies (plus vier auf der Flip Unit) zwischenspeichern lassen, während der Bestückkopf selbst noch am Bestücken ist. Die-Abholung vom Wafer und Die-Platzierung auf dem Substrat werden so voneinander entkoppelt und parallelisiert – die Bestück-Performance schließt damit deutlich zur SMT-Welt auf. Die neue innovative Lösung verarbeitet auf diese Weise bis zu 40.000 Flip-Chips beziehungsweise bis zu 50.000 Chips im Die-Attach-Verfahren oder bis zu 76.000 SMT-Bauelemente pro Stunde aus dem Gurt, und das bei einer Bestückgenauigkeit von bis zu 10 μm @ 3 σ.

Höchste Flexibilität für die Die-Verarbeitung

Die SIPLACE CA2 verfügt über ein Wechselsystem für bis zu 50 verschiedene Wafer, das konkurrenzlos ist. Der Wafer Swap erfolgt dabei in nur 10 Sekunden. Dieser Leistungsvorsprung senkt nicht nur die Investitionskosten deutlich, sondern spart auch wertvollen Platz auf dem Shopfloor ein, der nun für weitere schnelle Maschinen oder den Einsatz automatisierter Lager- und Transportsysteme zur Verfügung steht.

Kostensparend und nachhaltig

Die Abholung der Dies direkt vom Wafer macht den Prozessschritt des Die-Tapings komplett überflüssig, und der Wegfall des Gurtmaterials bietet gleich mehrere Vorteile. Je nach Volumen der Fertigung ergeben sich so Kosteneinsparungen bis in den Millionenbereich – für das Gurtmaterial selbst, aber auch für die Entsorgung oder die Lagerhaltung. Darüber hinaus leistet die Verarbeitung direkt vom Wafer einen Beitrag zur nachhaltigen Fertigung, denn es wird Gurtabfall in enormen Mengen vermieden.

Volle Rückverfolgbarkeit und Software-Integration

Die lückenlose Rückverfolgbarkeit von Bauelementen, wie sie in vielen Märkten bereits gefordert ist, stellt die Semiconductor-Welt auch heute meist noch vor große Herausforderungen. Hier bringt die SIPLACE Technologie den Fertigern mit „Full single die level traceability“ große Vorteile. So wird für jedes einzelne Die seine Pick-up- wie auch seine Bestückposition auf dem Board protokolliert – und das vollautomatisch.

Darüber hinaus bietet die SIPLACE Software schnelle Programm- und Produktwechsel, die Portierbarkeit von Bestückprogrammen an beliebige Maschinen gleichen Typs oder schnelles und umfassendes Substrate Mapping. Auch viele Applikationen der effizienz- und produktivitätssteigernden WORKS Software Suite sind für die SIPLACE CA2 verfügbar, beispielsweise für Setup Verification, Optimization und Logistics.

Gerade in der SiP-Fertigung ist die Kombination der SIPLACE CA2 mit dem hochgenauen Highspeed-Bestückautomat SIPLACE TX micron von ASMPT interessant: Beide Maschinen können in einer Fertigungslinie stehen und sich gegenseitig ergänzen – für höchste Genauigkeit, maximale Flexibilität und maximalen Ertrag.

Offene Schnittstellen für die intelligente Fertigung

Neben der für die Semiconductor-Fertigung wichtigen Schnittstelle SECS/GEM bietet die SIPLACE CA2 zudem den offenen Kommunikationsstandard IPC-2591 CFX – eine der Grundvoraussetzungen für die Umsetzung des ASMPT Konzepts der intelligenten Fertigung. Damit lässt sich nun auch für die Die-Verarbeitung die nahtlose Datenkommunikation sowohl auf dem Shopfloor als auch zu Factory- und Enterprise-Lösungen sicherstellen.