Feinleiter, Feinstleiter, Microleiter, Microfeinstleiter ...: Diese und ähnliche Begriffe umschreiben die Verfeinerung der Kupferstrukturen auf Leiterplatten. Objektivere Aussagen über die Leiterbahnstrukturen eines Layouts geben freilich erst konkrete Angaben in Mikrometern oder Milli-Inch (mil). Strukturen von 6 und 5 mil (150 µm und 125 µm) sind heute in der konventionellen SMD-Elektronik üblich, während 4 und 3 mil (100 µm und 75 µm) nur dort verwendet werden, wo hochpolige Fine-Pitch-Bauteile derart feine Strukturen erfordern. Doch es geht noch filigraner.

Mit der Einführung eines LDI-Prozesses hat Andus den Einstieg in die 2-mil-Technik vollzogen und ist jetzt imstande, auch Layouts mit nur 50 µm Strukturbreite zu fertigen. Solche 50-µm-Designs werden besonders dort benötigt, wo Micro-Ball-Grid-Arrays (µBGAs) oder Chip-Scale-Packages (CSPs) zu entflechten sind. Ein CSP mit 0,4-mm-Raster und zweireihig angeordneten 0,25-mm-Pads kann nur mit 2-mil-Strukturen vollständig entflochten werden. Vor allem Leiterplattensubstrate für Embedded-Computer nutzen diese Technik. Aber auch in der Sensorik sind 2-mil-Strukturen von Vorteil. So verdoppelt sich bei gleich bleibender Fläche die Windungszahl von Spulen gegenüber früheren 4-mil-Designs. Bei anderen Anwendungen bildet das 50-µm-Substrat ein Bindeglied zwischen Halbleiterstrukturen und konventionellen Leiterplatten.

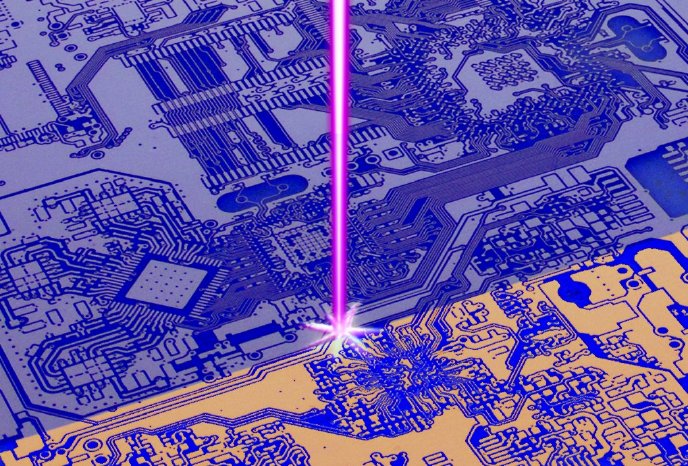

Laserdirektbelichter benötigen keine Masken, anstelle der bisherigen UV-Filmbelichtung übernimmt ein modulierter feiner Laserstrahl die zeilenweise Belichtung einer gesamten Leiterplatte. Die heutige LDI-Technik ist weit fortgeschritten, das Belichten eines Fertigungspanels dauert nur noch wenige Sekunden. Damit ist die Verarbeitung im Vergleich zu konventioneller Technik auch noch schneller. Außerdem ist die LDI-Technik in der Lage, individuelle Muster aufs Substrat zu schreiben, etwa, um Positionierungsfehler zu kompensieren, oder individuelle Layouts mit fortlaufender Kennnummer zu gewährleisten.