Der erste auf der AURIX-Architektur basierende Mikrocontroller mit der Bezeichnung TC275T enthält drei TriCore-Kerne der Version 1.6. Zwei davon sind auf maximale Leistung optimiert (High-Performance TriCore-CPU 1.6P)und können bis zu drei Befehle in einem Zyklus bei einer maximalen Taktfrequenz von 200 MHz abarbeiten. Beim dritten Kern, einer High-Efficiency TriCore-CPU 1.6E, stehen ein möglichst geringer Energieverbrauch und ein effizienter Datenaustausch mit der Peripherie im Vordergrund. Er kann höchstens einen Befehl pro Zyklus abarbeiten und wird aktuell mit maximal 200 MHz getaktet.

Die UDE 3.3 erlaubt die Steuerung und Kontrolle der unterschiedlichen TriCore-CPUs innerhalb einer Bedienoberfläche. Unterstützt wird dies durch einen flexiblen Multicore-Program-Loader, der das Laden von Programm-Code und Daten sowie Symbolinformationen getrennt für jeden Core ermöglicht. Die Steuerung der Cores erfolgt über einen Multicore-Run-Control-Manager, der eine Definition von Core-Gruppen bietet. Damit ist eine sehr flexible Kontrolle des Laufzeitverhaltens der komplexen Architektur möglich.

Bei Bedarf ist mit der UDE 3.3. auch eine Programmentwicklung für das integrierte Hardware Security Modul (HSM) möglich. Dieses bietet Fahrzeugherstellern einen konfigurierbaren Schutz der Systemintegrität ihrer Steuergeräte und ist durch seine Flexibilität auch für künftige Sicherheitsanforderungen gerüstet. Außerdem unterstützt die UDE 3.3. die gegenüber der AUDO-Familie bis zu 20mal schnellere Programmierung des auf 4 MByte vergrößerten FLASH-Speichers.

Die UDE 3.3. erleichtert auch das Debuggen von Programmcode auf dem neuen leistungsfähigen Generic Timer Module (GTM), mit dem sich mit Hilfe eines eigenen Befehlssatzes unterschiedliche Aufgaben aus den Bereichen Zeitmessung, erfassen/vergleichen von digitalen Eingangssignalen bis hin zu komplexen Algorithmen wie Pulsweitenmodulation (PWM) lösen lassen.

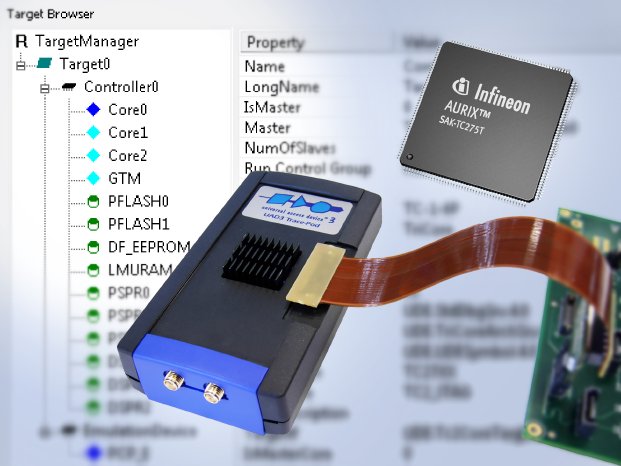

Das von der bisherigen TriCore-Architektur für die AUDO-Familie bekannte ausgefeilte On-Chip-Debug-System (OCDS) wurde für die AURIX-Familie weiter optimiert und an die Erfordernisse von MultiCore-Debugging angepasst, wobei die neuen zusätzlichen Optionen sowohl durch die UDE 3.3. als auch durch PLS' Universal Access Device-Familie UAD2 bzw. UAD3+ uneingeschränkt unterstützt werden.

Bezüglich Programm-, Daten- und Bus-Trace setzt Infineon auch bei der neuen AURIX-Architektur auf die bereits bewährten Emulation Devices (ED) mit Multi Core Debug System (MCDS). Die Emulation Devices sind zum Produktionschip pinkompatibel, enthalten jedoch eine ausgefeilte Beobachtungs- und Triggerlogik sowie aktuell bis zu 2 MByte Emulationsspeicher. Die Programmierung der Emulationslogik kann komfortabel mit dem in die UDE 3.3. integrierten und weiterentwickelten Universal Emulation Configurator erfolgen, da dieser eine grafische Konfiguration von Messaufgaben bietet, bei der Signale und Aktionen über eine State-Machine verknüpft werden.

Um die Testbarkeit der neuen AURIX-Mikrocontroller mit Multicore-Architektur weiter zu steigern, hat Infineon erstmalig auch eine Aurora GigaBit Trace-(AGBT-)Schnittstelle am Emulation Device implementiert. Damit kann der Trace-Speicher durch Anschluss externer Hardware drastisch vergrößert werden, wodurch wiederum die Bewältigung von High-End-Trace-Aufgaben mit großen Datenmengen, zum Beispiel Code Coverage, möglich wird. Ein 2,5-GB/s-Aurora-Interface setzt allerdings eine entsprechend leistungsfähige Hardware für Signalaufnahme, Signalkonditionierung und Vorverarbeitung am Target voraus.Für das UAD3+ von PLS ist deshalb nicht nur ein Trace-Pod mit AGBT-Schnittstelle verfügbar, es kann auch mit bis zu 4 GByte externen Trace-Speicher ausgerüstet werden.

Wie wichtig die frühzeitige Verfügbarkeit optimierter Test- und Debug-Tools für die erfolgreiche Markteinführung neuer leistungsfähiger MultiCore-Mikrocontroller-Familien ist, erklärt Gerd Punsmann, Tool-Manager 32-Bit-Automotive Mikrocontroller bei Infineon. "Wir wollen, dass unsere Kunden am Tag der Markteinführung unserer neuen AURIX-Mikrocontroller mit Multicore-Architektur mit der Entwicklung von Applikationen beginnen können. Damit das reibungslos funktioniert, muss eine umfangreiche Toollandschaft, wie beispielsweise von unserem Partner PLS, zeitnah verfügbar sein."

Heiko Rießland, Product Marketing Manager bei PLS, ergänzt: "Die lange und enge Kooperation zwischen Infineon und PLS garantiert Anwendern der AURIX-Mikrocontrollerfamilie ein Höchstmaß an Flexibilität und Sicherheit, da Sie bereits mit der Verfügbarkeit der ersten Chips auf ein gleichermaßen leistungsfähiges wie praxiserprobtes Debug-Werkzeug zurückgreifen können."