The All Programmable SoCs of the Xilinx Zynq-7000 family of devices combine for the first time dual-core ARM® Cortex™-A9 architecture with the functionality of complex Field Programmable Gate Arrays (FPGAs) on a single chip. In order to simplify development of appropriate powerful multi-core software, the UDE 4.4.3, among other things, enables users a flexible control of both cores within a consistent user interface. The cores can also be synchronously started and stopped, independently from each other or by grouping together in a so-called run control group.

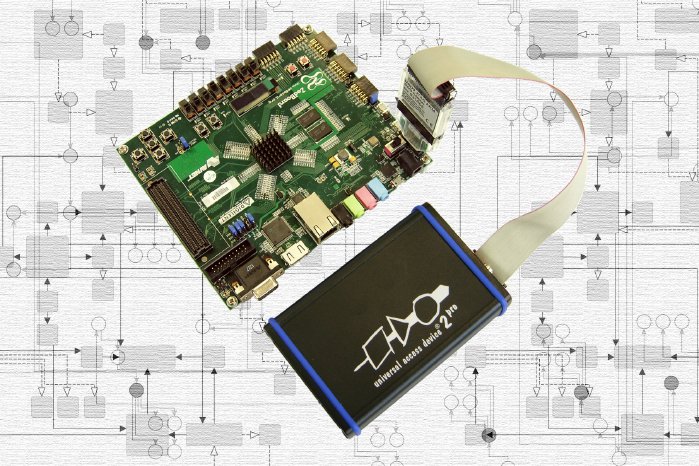

Furthermore, the full support of all trace function units included on the SoCs ensures an especially efficient hard/software co-debugging. The UDE 4.4.3 support includes internal Program Trace Macrocell (PTM) for fast program trace in an on-chip memory as well as Coresight™ Instrumentation Trace Macrocell (ITM) that is important for troubleshooting and program measurements. A special Fabric Trace Macrocell (FTM) has also been integrated on the Zynq-7000 SoC devices for the output of internal signals from the FPGA logic into the common trace data stream. This unit, which simplifies debugging of the complex overall system, can also be configured by the UDE. Additionally, with PLS' Universal Access Device 3+ (UAD3+), a powerful hardware tool with 4 GB memory is available for recording external trace data. Besides trace, the debugger also enables very precise program runtime measurements by using the performance counter integrated on the SoC.

The system typically starts using a boot loader mechanism from an external flash memory. This can be programmed via the debugger. Connection of the UDE 4.4.3 with the Zynq-7000 SoC is achieved via JTAG. A digitally isolated connection to the target is also optionally possible with the Universal Access Device (UAD) family. Furthermore, a full Eclipse integration with complete cross-debugger functionality is included in the UDE 4.4.3.